BaseJump: Building the DNA For Open Source ASIC Systems

Brought to you by Taylor's Bespoke Silicon Group.

|

|

|

Our vision is to create a path that allows researchers to

prototype their ideas without worrying about all of the

intricacies of I/O, packaging, PC board design and FPGA coding.

Our goal is to shave 10-15 people-years off of a typical ASIC prototype

development process, and at the same time enable artifacts that are

of superior performance to what most research groups would have the resources to do.

We have implemented a complete system that extends from the pad

ring of the chip all the way out. You just need to design your

verilog to connect to our simple interface, and then

make use of the pre-built components that we have developed and tested.

Push it through IC Compiler, PrimeTime and Calibre to a tapeout. The rest

of the way has already been thought out.

Current Users:

University of Washington

University of Utah

University of Toronto

Princeton University

University of Illinois Urbana Champagne

Massachusetts Institute of Technology

University of California, San Diego

U of Cambridge

Cornell

U. Michigan

Prof. Michael Taylor

Bespoke Silicon Group

University of Washington CSE and EE

|

BaseJump Projects

BaseJump STL (Standard Template Library) for SystemVerilog

BaseJump Manycore

BlackParrot RISC-V Linux Capable Multicore

BaseJump ASIC Sockets

BaseJump ASIC Motherboards

BaseJump FPGA Bridge

BaseJump RoCC Doc

RV-IOV: RISC-V IO Virtualization

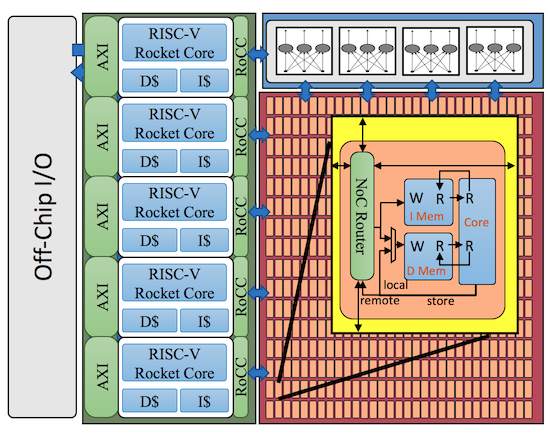

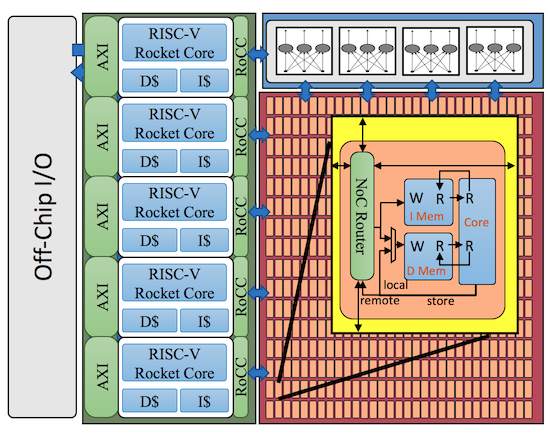

Most of these components have been combined and used in the

511 RISC-V Core Open Source Celerity chip which was taped out

in TSMC 16nm FinFet technology:

BaseJump STL: A standard library for SystemVerilog

This library has many of the standard components that you use in hardware design.

But these ones are nicely parameterized, and try to use latency-insensitive

interfaces where it does not hurt performance.

We are always looking for those who want to contribute, write testing code,

or offer feedback.

These are good projects for students looking for summer projects.

See the repository here.

BaseJump ASIC Socket

The BaseJump ASIC Socket interface provides a standardized interface for new ASIC accelerators to use, allowing fast time to market and low NRE.

You match up your RTL with our Network-On-Chip interface, and then you can use our package, board, and PHY/MAC layer, provided in portable SystemVerilog for both FPGA and ASIC, to make a complete system!

You can use our RTL, socket interface, our pad ring, our package, and our board all independently of each other. But you will minimize design time and cost if you use them all together!

Our socket interface, pad ring, package and board are all jointly optimized for signal integrity.

See detailed information on:

BaseJump Socket 352

BaseJump Socket 355

BaseJump ASIC MotherBoards

We also provide standardized ASIC motherboards for use in rapidly bootstrapping your systems. These comply with the various BaseJump ASIC socket interfaces.

See these links:

BaseJump Socket 352 Motherboards

BaseJump LVCMOS Link (ASIC-to-ASIC and FPGA-to-FPGA Bridge)

The BaseJump FPGA Bridge is designed to work with BaseJump Socket.

It is synthesizeable SystemVerilog that implements a high-speed DDR source

synchronous communication channel (PHY, link and MAC layer.)

It is designed to be instantiated into an ASIC, and allows high speed

communication through the BaseJump BGA package to another FPGA.

We also support, for Double and Real Trouble, an additional hop that goes from

a "gateway" FPGA over FMC to an ML-605 or Zedboard

which hosts the DRAM memory system and/or and PCI-E host to a PC. The idea is

that if you reuse the BaseJump Socket

Interface, you can attached your RTL verilog to a working I/O system

with very little effort.

See BaseJump STL bsg_link.

Note we have Spartan-6 specific code for the bridge that uses the FPGA SerDes. Send us an email and we will post it.

BaseJump BSG PCI Express Implementation

This module allows an Virtex-6 ML-605 board to communicate with Linux 2.6 via the PCI Express connector.

The abstraction is a number of flow-controlled

FIFOs that are mapped into user space Linux. Your user code reads and writes to the FIFOs

via memory-mapped I/O.

Source code is available here: bitbucket.org/taylor-bsg/bsg_pci

UCSD has a PC<-->FPGA board infrastructure called

RIFFA. It has a wider variety of

supported boards, but focuses on DMA from DRAM. We would guess that the latency

is higher but that the throughput is better.

The BaseJump RV-IOV (RISC-V Virtualization)

Further Steps

Contact information: Contact Prof. Michael B. Taylor for more information.

This work funded by National Science Foundation Grant #1059333

(Collaborative Research: II-NEW: Prototyping Platform to Enable Power-Centric Multicore Research).

Thanks to Prof. Chris Batten of Cornell and Prof. Steven Swanson for feedback and collaboration.

Thanks to Ningxiao Sun for his stellar Double Trouble PCB design, and for Scott Davidson, Shengye Wang, Luis Vega

and Bunnie Huang for all of their engineering assistance on the board!

Terms: You may use this infrastructure at your own risk, and as long as you

agree not to hold us liable for any issues that occur as a result of your use of the infrastructure.

This infrastructure is intended for prototyping uses only and has not been validated for use in any

product.