|

Key:

| ||||||||||||||||||||||||||||||||||||||

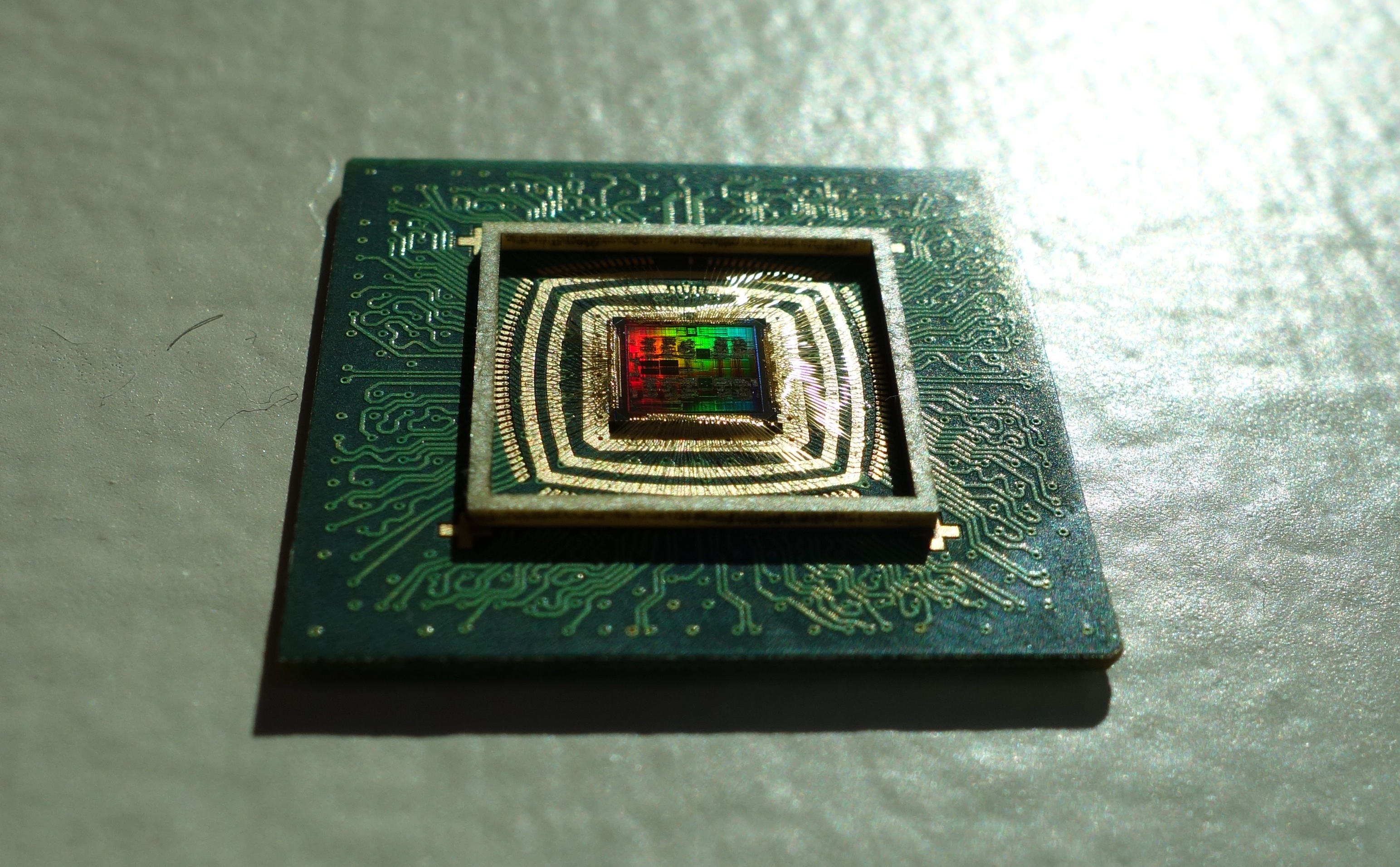

(Click on the pictures for larger view.)

Click here for zoomed-in photos of the chip.

Shmoo plot confirming operation at 280 MHz @ 1.8V and 370 MHz @ 2.4V

Our High-Speed Singled-Ended DDR I/O (using off-the-shelf 3.3V TTL) has been confirmed to work at ~390 MHz with 16mA outputs.

Back to BaseJump mainpage.

.

.